# 50V , R1 = 4.7 k $\Omega$ , R2 = 4.7 k $\Omega$ NPN / NPN Digital Transistors

### 1. Product profile

#### 1-1.General description

The UMH15NTH of digital transistors is designed to replace a single device and its external resistor bias network. The bias resistor transistor contains a single transistor with a monolithic bias network consisting of two resistors; a series base resistor and a base—emitter resistor. The UMH eliminates these individual components by integrating them into a single device. The use of a UMH can reduce both system cost and board space.

#### 1-2. Features

- BV<sub>CC</sub> > 50V

- I<sub>C</sub> = 100mA high collector current

- Built-In bias resistors  $R_1 = 4.7K\Omega$ ,  $R_2 = 4.7K\Omega$

- Pair of PNP transistors that are intrinsically matched

- Simplifies circuit design

- Reduce board space

- Reduce component count

#### 1-3. Applications

- Inverter

- Interface

- Driver

#### 1-4. Mechanical characteristics

- Molded SOT-363 package

- Packing:tape and reel

- Flammability rating UL 94V-0

- Halogen free

- Moisture sensitivity levels (MSL): Level 1

SOT363

# 50V , R1 = 4.7 k $\Omega$ , R2 = 4.7 k $\Omega$ NPN / NPN Digital Transistors

### 2. Maximum ratings

#### Table 1. maximum ratings

| Parameter                 | Symbol          | Value       | Units |

|---------------------------|-----------------|-------------|-------|

| Supply voltage            | V <sub>CC</sub> | 50          | V     |

| Input voltage             | V IN            | -10 to 30   |       |

| Output current            | Ιο              | 100         | mA    |

| Max. collector current    | Ic              |             |       |

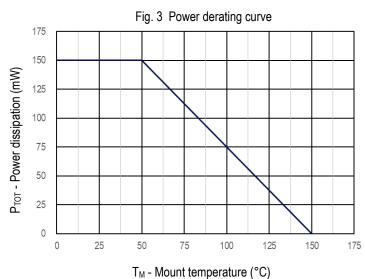

| Total power dissipation   | P tot           | 150         | mW    |

| Junction temperature      | Тј              | -55 to +150 | °C    |

| Storage temperature range | T stg           | -55 to +150 |       |

### 3. Electrical characteristics

#### Table 3. Electrical characteristics

| Parameter      | Symbol               | Condition                                         | Min. | Тур. | Max. | Units |

|----------------|----------------------|---------------------------------------------------|------|------|------|-------|

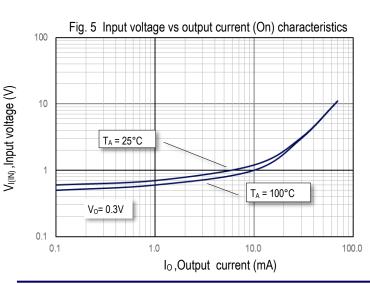

| Input voltage  | V <sub>IN -OFF</sub> | $V_{CC}$ = 5V , $I_O$ = 100uA                     | 0.5  | -    | -    | V     |

|                | V <sub>IN-On</sub>   | $V_0 = 0.3V$ , $I_0 = 5mA$                        | -    | -    | 1.3  |       |

| Output voltage | V <sub>O-ON</sub>    | $I_{O} = 10 \text{mA}$ , $I_{IN} = 0.5 \text{mA}$ | -    | -    | 0.3  |       |

| Input current  | I <sub>IN</sub>      | V <sub>IN</sub> = 5.0V                            | -    | -    | 1.8  | mA    |

| Output current | I <sub>O(OFF)</sub>  | $V_{CC} = 50 Vdc, V_I = 0 V$                      | -    | -    | 0.5  | uA    |

### 4. On characteristics

#### Table 5. On characteristics

| Parameter        | Symbol                          | Condition                              | Min. | Тур. | Max. | Units |

|------------------|---------------------------------|----------------------------------------|------|------|------|-------|

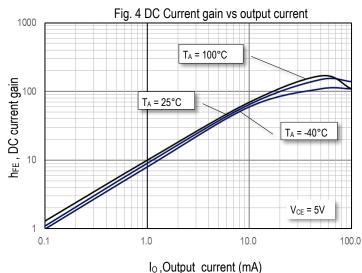

| DC current gain  | h <sub>FE</sub>                 | $I_C = 10 \text{mA}, V_O = 5 \text{V}$ | 30   | -    | -    | -     |

| Input resistance | R 1                             | -                                      | 3.29 | 4.7  | 6.11 | ΚΩ    |

| Resistance ratio | R <sub>2</sub> / R <sub>1</sub> | -                                      | 8.0  | 1    | 1.2  | -     |

### 5. Small signal characteristics

#### Table 6. small signal characteristics

| Parameter                      | Symbol | Condition                                                    | Min. | Тур. | Max. | Units |

|--------------------------------|--------|--------------------------------------------------------------|------|------|------|-------|

| Current gain bandwidth product | f⊤     | $I_O = 5\text{mA}, V_{CE} = 10\text{V}, f=100\text{MHz}$     | -    | 250  | -    | MHz   |

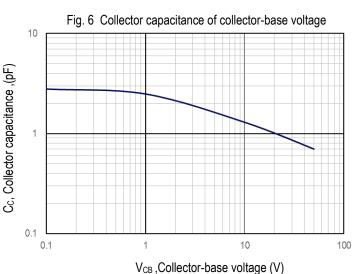

| Collector capacitance          | Cc     | V <sub>CB</sub> = 10 V; I <sub>E</sub> = ie = 0 A; f = 1 MHz | -    | -    | 2.5  | pF    |

# 50V , R1 = 4.7 k $\Omega$ , R2 = 4.7 k $\Omega$ NPN / NPN Digital Transistors

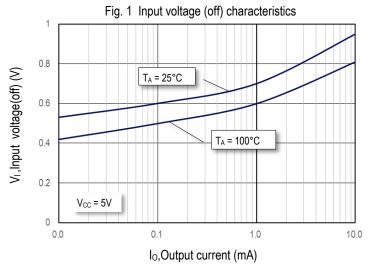

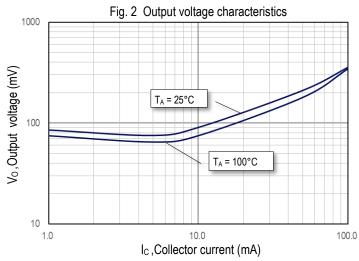

### 6. Rating and characteristics curve

# 50V , R1 = 4.7 k $\Omega$ , R2 = 4.7 k $\Omega$ NPN / NPN Digital Transistors

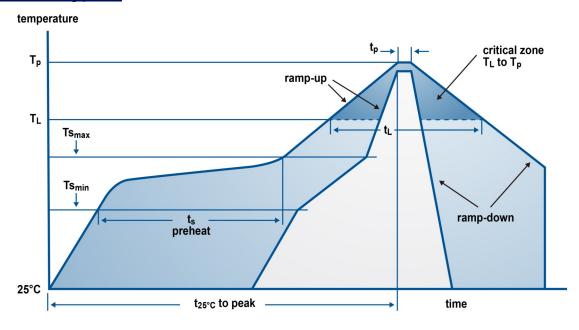

### 7. Recommended reflow soldering profile

#### 7-1. Limiting value

The below temperature profile for moisture sensitivity characterization is based on the IPC/JEDEC joint industry standard: J-STD-020D-01.

| Profile Feature                                  | SnPb eutectic assembly | Pb-free assembly  |

|--------------------------------------------------|------------------------|-------------------|

| Average ramp-up rate (Tsmax to Tp)               | 3 °C/s maximum         | 3 °C/s maximum    |

| Preheat                                          |                        |                   |

| Temperature minimum (Tsmin)                      | 100 °C                 | 150 °C            |

| Temperature maximum (Tsmax)                      | 150 °C                 | 200 °C            |

| Time (tsmin to tsmax)                            | 60 s to 120 s          | 60 s to 180 s     |

| Time maintained above                            |                        |                   |

| Temperature (TL)                                 | 183 °C                 | 217 °C            |

| Time (tL)                                        | 60 s to 150 s          | 60 s to 150 s     |

| Peak/classificationtemperature(T)                | 235 °C                 | 260 °C            |

| Number of allowed reflow cycles                  | 3                      | 3                 |

| Time within 5 °C of actual peak temperature (tp) | 10 s to 30 s           | 20 s to 40 s      |

| Ramp-down rate                                   | 6 °C/s maximum         | 6 °C/s maximum    |

| Time 25 °C to peak temperature                   | 6 minutes maximum      | 8 minutes maximum |

#### 7-2. Reflow soldering profile

All information hereunder is per Futurewafer Tech' best knowledge. In case Futurewafer Tech has tested the product, This documentation reflects The outcome of the analysis of the actually tested parts only. This document does not provide for any representation or warranty express or implied by Futurewafer Tech. applications and test results, analysis or assessments that are described herein are for illustrative purposes only. Futurewafer Tech makes no representation or warranty neither that such applications will be suitable for the specified use nor that the information, test results, analysis or assessments are reliable without further testing or modification through customer.

# 50V , R1 = 4.7 k $\Omega$ , R2 = 4.7 k $\Omega$ NPN / NPN Digital Transistors

## 8. Package information

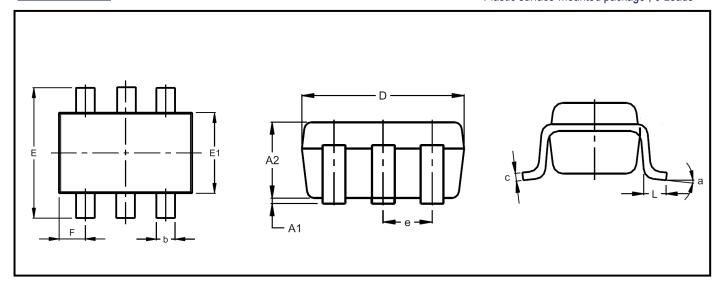

#### 8-1. Dimension

Plastic surface-mounted package; 6 Leads

| Table 7 | . Package si | ummary |      |      |     |     |      |      |      | Dime | ension in mm |

|---------|--------------|--------|------|------|-----|-----|------|------|------|------|--------------|

| Dim     | <b>A</b> 1   | A2     | b    | С    | D   | E   | E1   | е    | F    | L    | а            |

| Min     | 0.00         | 0.9    | 0.10 | 0.10 | 1.8 | 2.0 | 1.15 | -    | 0.40 | 0.20 | -            |

| Тур     | -            | -      | -    | -    | -   | -   | -    | 0.65 | -    | -    | -            |

| Max     | 0.10         | 1.0    | 0.30 | 0.22 | 2.2 | 2.2 | 1.35 | -    | 0.45 | 0.40 | 8°           |

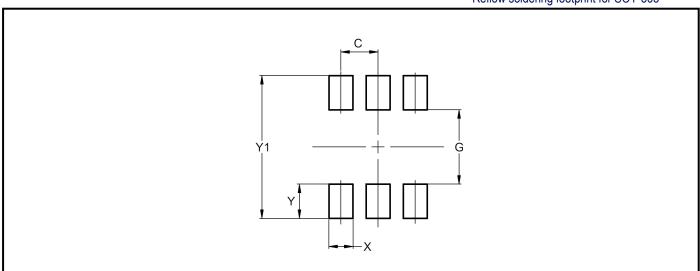

#### 8-2. PCB Pad layout recommendation

Reflow soldering footprint for SOT-363

| Table 8. layout s | ummary |      |      |      | Dimension in mm |

|-------------------|--------|------|------|------|-----------------|

| Dim               | С      | G    | Х    | Υ    | <b>Y</b> 1      |

| Value             | 0.65   | 1.30 | 0.42 | 0.60 | 2.50            |

# 50V , R1 = 4.7 k $\Omega$ , R2 = 4.7 k $\Omega$ NPN / NPN Digital Transistors

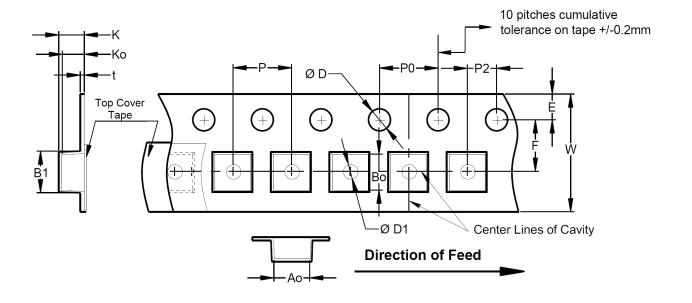

### 9. Packing

### 9-1. Taping and reel specification

| Taping width | Tape orientation  |

|--------------|-------------------|

| 8 mm         |                   |

|              | Direction of feed |

#### 9-2. Embossed carrier tape specification

Table 9. tape summary Dimension in mm

| Dimension | W         | B1                                                                                                                 | D        | D1   | E     | F     | K    | Р     | P0    | P2    | t    | W    |

|-----------|-----------|--------------------------------------------------------------------------------------------------------------------|----------|------|-------|-------|------|-------|-------|-------|------|------|

| Value     | 8         | 4.5                                                                                                                | 1.5+     | 0.35 | 1.75  | 3.5   | 2.4  | 4.0   | 4.0   | 2.0   | 0.4  | 8    |

|           | mm        | Max                                                                                                                | 0.1/-0.0 | Min. | ±0.10 | ±0.05 | Max. | ±0.10 | ±0.10 | ±0.05 | Max. | ±0.3 |

| A0 /      | Determin  | Determined by component size. The clearance between the component and the cavity must comply to the rotational and |          |      |       |       |      |       |       |       |      |      |

| B0 /      | lateral m | ateral movement requirement provided in figures in the "maximum component movement in tape pocket" section.        |          |      |       |       |      |       |       |       |      |      |

| K0        |           |                                                                                                                    |          |      |       |       |      |       |       |       |      |      |

# 50V , R1 = 4.7 k $\Omega$ , R2 = 4.7 k $\Omega$ NPN / NPN Digital Transistors

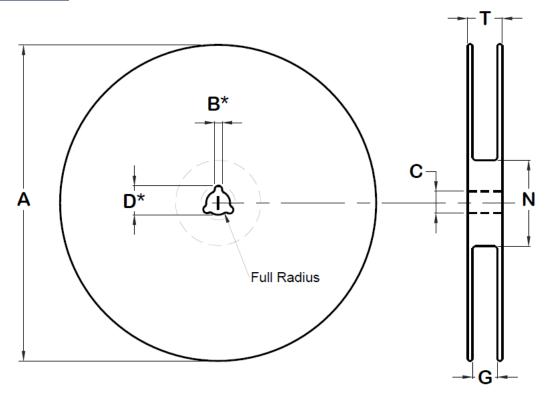

## 10. Surface mount reel specification

#### 10-1. Reel specification

Table 10. Reel information

Unit: mm

| Dimension | Tape width | Reel size | Α   | В      | С        | D    | N  | G          | Т    |

|-----------|------------|-----------|-----|--------|----------|------|----|------------|------|

| Value     | 8 mm       | 7"        | 178 | 2.0    | 13       | 20.5 | 55 | 8.4        | 14.4 |

|           |            |           | ±2  | +0.5-0 | +0.5-0.2 | ±0.2 | ±5 | +1.5/ -0.0 | Max. |

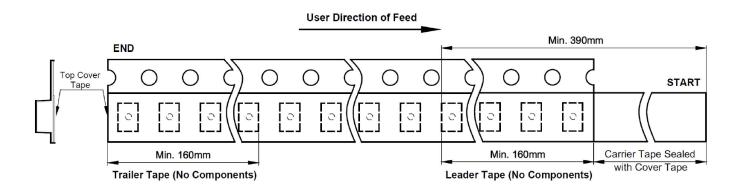

#### 10-2. Tape leader and trailer specification

# 50V , R1 = 4.7 k $\Omega$ , R2 = 4.7 k $\Omega$ NPN / NPN Digital Transistors

### 11. Ordering information

Table 11. Ordering information

| Part number | Package name | Description                              | Packing                                  |

|-------------|--------------|------------------------------------------|------------------------------------------|

| UMH15NTH    | SOT-363      | Plastic surface-mounted package; 6 leads | 3,000 P <sub>CS</sub> / 7" tape and reel |

## 12. Marking information

Table 12. Marking codes

| Part number | Marking code |

|-------------|--------------|

| UMH15NTH    | H15          |

#### 13. Pinning information

Table 13. Pinning information

| Pin | Symbol | Description | Simplified outline | Graphic symbol |  |

|-----|--------|-------------|--------------------|----------------|--|

| 1   | E 1    | Emitter 1   | 6 5 4              | 6 5 4          |  |

| 2   | B 1    | Base 1      | 6 5 4              | R1 \$ R2       |  |

| 3   | C 2    | Collector 2 | Mankina            | TR1 TR2        |  |

| 4   | E 2    | Emitter 2   | Mai Kiliy          |                |  |

| 5   | B 2    | Base 2      |                    | R2 \$ R1       |  |

| 6   | C 1    | Collector 1 |                    | 1 2 3          |  |

# 50V , R1 = 4.7 k $\Omega$ , R2 = 4.7 k $\Omega$ NPN / NPN Digital Transistors

#### 14. Legal information

#### **Definitions**

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Futurewafer does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### **Disclaimers**

<u>Limited Warranty And Liability</u> — Information in this document is believed to be accurate and reliable. However, Futurewafer does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Futurewafer takes no responsibility for the content in this document if provided by an information source outside of Futurewafer. In no event shall Futurewafer be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Not withstanding any damages that customer might incur for any reason whatsoever, Futurewafer's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the terms and conditions of commercial sale of Futurewafer.

Right to make changes — Futurewafer reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication here of.

<u>Suitability for use</u> — Futurewafer products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Futurewafer product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Futurewafer and its suppliers accept no liability for inclusion and/or use of Futurewafer products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications — applications that are described herein for any of these products are for illustrative purposes only. Futurewafer makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the Design and operation of their applications and products using Futurewafer products, and Futurewafer accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Futurewafer product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Futurewafer does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). customer is responsible for doing all necessary testing for the customer's applications and products using Futurewafer products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Futurewafer does not accept any liability in this respect.

<u>Export control</u> — This document as well as the item(s) described herein may be subject to export control regulations. export might require a prior authorization from competent authorities.

<u>Translations</u> — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

# 50V , R1 = 4.7 k $\Omega$ , R2 = 4.7 k $\Omega$ NPN / NPN Digital Transistors

#### 15. Revision history

Table 14. Revision history

| Version | Document ID | Release date | Change notice  | Basis  |

|---------|-------------|--------------|----------------|--------|

| A       | F51830X     | 03-Aug-2018  | New develop    | Market |

| 4.0     | _           | 24-Mar-2023  | Update version | System |

#### FutureWafer Tech Co.,Ltd 台灣未來芯科技股份有限公司

T: +886-3-3350161 / F: +886-3-3350172 / Email: sales@futurewafer.com.tw 11F., No.286, Sec.3, Sanmin Rd., Taoyuan Dist., Taoyuan City 33042, Taiwan

FutureWafer and are Trademarks of FutureWafer Tech co.,Itd or Its Subsidiaries in The Taiwan And/or Other Countries.

FuturewWafer Tech Reserves The Right to Make Changes Without Further Notice to Any Products Herein. FutureWafer Tech Makes no Warranty, Representation or Guarantee Regarding The Suitability of Its Products For Any Particular Purpose, Nor Does FutureWafer Tech Assume Any Liability Arising Out of The Application or Use of Any Product or Circuit, And Specifically Disclaims Any And aAll Liability, Including Without Limitation Special, Consequential or Incidental Damages. FutureWafer Tech Does Not Convey Any License Under Its Patent Rights Nor The Rights of Others.